偽隨機(jī)測(cè)試生成方法是一種測(cè)試方法?它可以生成符合隨機(jī)特征數(shù)據(jù)的測(cè)試圖形?這種方法通常由微處理器的測(cè)試軟件算法或?qū)S玫钠蠝y(cè)試電路來生成?比較容易?探針臺(tái)等設(shè)備若有足夠長(zhǎng)的測(cè)試圖形?就能夠產(chǎn)生比較高的故障覆蓋率?

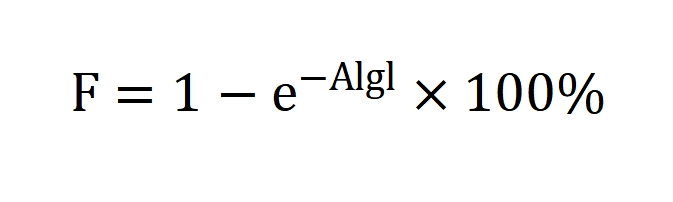

故障覆蓋率F與測(cè)試圖形長(zhǎng)度L之間的關(guān)系可以表示為下面公式?式中A對(duì)于每一個(gè)給定的電路來說是一個(gè)常數(shù)?

偽隨機(jī)測(cè)試要滿足要求故障覆蓋率;測(cè)試圖形長(zhǎng)度該取多少;生成可靠且易于實(shí)現(xiàn)的偽隨機(jī)序列等?

生成偽隨機(jī)序列通常采用兩種方法:

(1)同余法;

(2)用無輸人的線性反饋寄存器構(gòu)成偽隨機(jī)序列生成電路?

傳統(tǒng)結(jié)構(gòu)的偽隨機(jī)生成方法存在以下兩個(gè)缺點(diǎn):

(1)隨機(jī)測(cè)試圖形大量不斷變化的位碼使得測(cè)試功耗大大增加;

(2)偽隨機(jī)測(cè)試中常用的是固定型故障模型?此模型難以描述CMOS深亞微米中的缺陷?這促使偽隨機(jī)測(cè)試技術(shù)不斷發(fā)展?為此在探針臺(tái)等設(shè)備內(nèi)建自測(cè)試技術(shù)中出現(xiàn)了一種全新的測(cè)試生成電路?即輸入單個(gè)位變化的偽隨機(jī)測(cè)試生成電路?該電路可以同時(shí)生成檢測(cè)固定型故障以及CMOS其他類型故障的測(cè)試圖形?